- 您现在的位置:买卖IC网 > Sheet目录3832 > PIC16C924-04/L (Microchip Technology)IC MCU OTP 4KX14 LCD DVR 68PLCC

Micrel, Inc.

KSZ8873MLL/FLL/RLL

September 20, 2013

111

Revision 1.6

Reset Timing

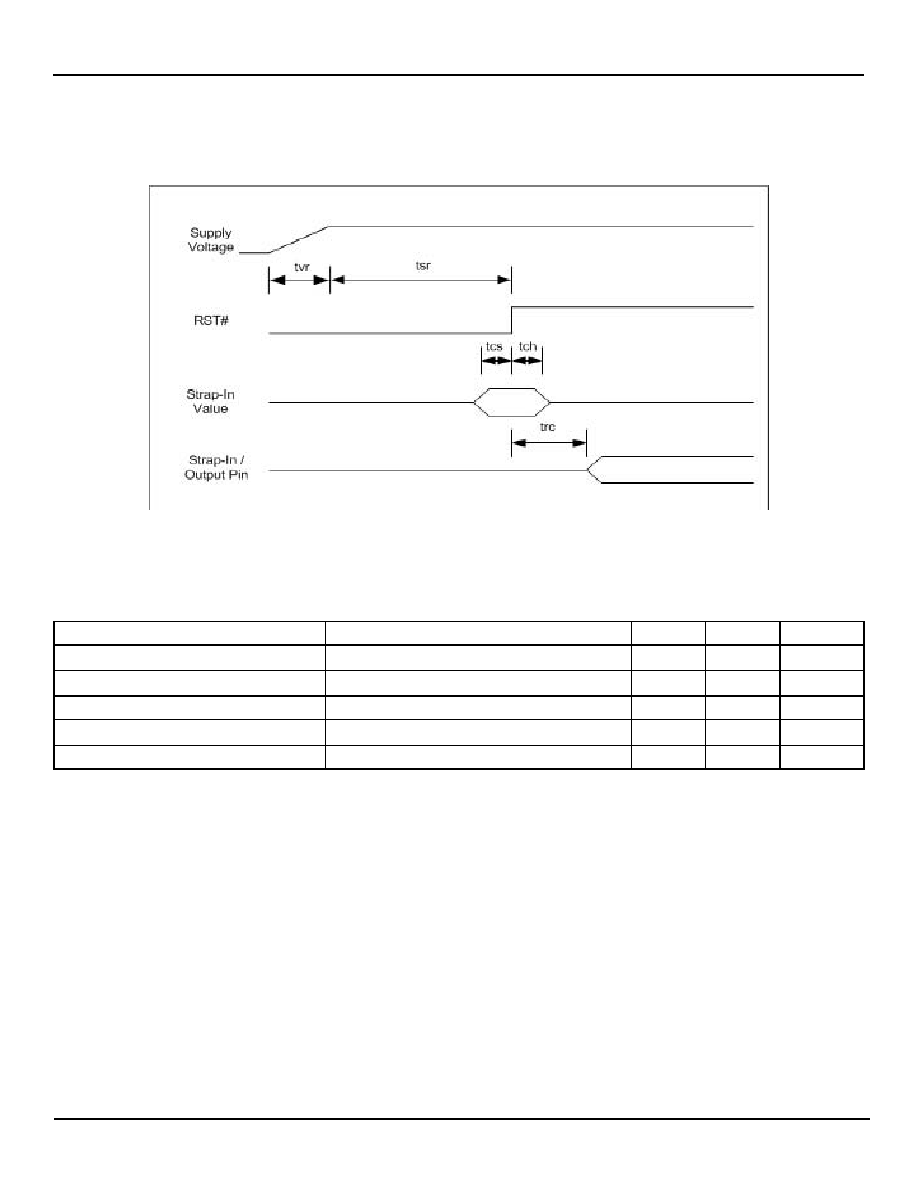

The KSZ8873MLL/FLL/RLL reset timing requirement is summarized in Figure 31 and Table 32.

Figure 31. Reset Timing

Table 32. Reset Timing Parameters

Symbols

Parameters

Min.

Max.

Units

tSR

Stable Supply Voltages to Reset High

10

ms

tCS

Configuration Setup Time

50

ns

tOH

Configuration Hold Time

50

ns

tRC

Reset to Strap-In Pin Output

50

s

tVR

3.3V Rise Time

100

s

Note:

After the de-assertion of reset, it is recommended to wait a minimum of 100s before starting programming on the managed interface (I

2C slave, SPI

slave, SMI, MIIM).

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16F767-I/SO

IC PIC MCU FLASH 8KX14 28SOIC

PIC24FJ64GA310-I/PF

MCU 16BIT 64KB FLASH 100TQFP

DSPIC33FJ64GP202-E/MM

IC DSPIC MCU/DSP 64K 28-QFN

PIC16F876A-I/ML

IC MCU FLASH 8KX14 A/D 28QFN

PIC16F876A-I/SO

IC MCU FLASH 8KX14 EE 28SOIC

PIC16F876A-I/SP

IC MCU FLASH 8KX14 EE 28DIP

AT87C51RD2-3CSUM

IC 8051 MCU 64K OTP 40MHZ 40DIP

DSPIC33FJ64MC802-I/SO

IC DSPIC MCU/DSP 64K 28-SOIC

相关代理商/技术参数

PIC16C924-04/PT

功能描述:8位微控制器 -MCU 7KB 176 RAM 52 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C924-04I/L

功能描述:8位微控制器 -MCU 7KB 176 RAM 52 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C924-04I/PT

功能描述:8位微控制器 -MCU 7KB 176 RAM 52 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C924-08/L

功能描述:8位微控制器 -MCU 7KB 176 RAM 52 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C924-08/PT

功能描述:8位微控制器 -MCU 7KB 176 RAM 52 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C924-08I/L

功能描述:8位微控制器 -MCU 7KB 176 RAM 52 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C924-08I/PT

功能描述:8位微控制器 -MCU 7KB 176 RAM 52 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C924CL

制造商:MICROCHIP 功能描述:New